# CURRENT DIFFERENCING CMOS VOLTAGE-CONTROLLED TRANSCONDUCTOR AND RESISTOR

Nikša Tadić, Elektrotehnički fakultet u Podgorici Desa Gobović, West Virginia State Community and Technical College Mirjana Banjević, Elektrotehnički fakultet u Podgorici

**Abstract** - The presented CMOS voltage-controlled transconductor and floating resistor are based on the current difference of two nonsaturated MOSFETs with equal sourceto-drain voltages. A new type of the summing-differencing current circuit is introduced. The circuits operate at a supply of  $\pm 1.5$  V. Simulations show nonlinearities below 1.4 % for input voltage swings up to  $\pm 0.5$  V, and 5 % frequency bandwidths above 70 MHz.

## **1. INTRODUCTION**

Voltage-controlled transconductor (VCT) [1] and voltage-controlled resistor (VCR) [2] employ the current difference of two nonsaturated MOSFETs with equal drainto-source voltages. Two source-coupled pairs degenerated by nonsaturated MOSFETs are used. Transconductances (resistances) are independent of the MOSFETs' threshold voltages. Their values can be varied by the difference of two control voltages over a wide range without affecting the input voltage range. They are insensitive to substrate noise and to noise common to the control voltages. Both the positive and the negative transconductances (resistances) can be obtained. However, the designs [1] and [2] are based on the assumption that the gate-to-source voltages of the input source-followers carrying different currents are equal. They can be made only nearly equal in the case of large W/L ratios of the MOSFETs used. This is the main source of the linearity errors in [1] and [2]. Another VCT and floating VCR CMOS architecture suitable for low-voltage operation using current differencing principle and avoiding considered drawback is presented in this paper. A novel type of summing-differencing current circuit (SDCC) is also introduced and used as a building block of both the VCT and the VCR.

# 2. CIRCUIT DESCRIPTION

The drain currents of the matched nonsaturated pchannel MOSFETs  $M_1$  and  $M_2$  with common substrate [3] are given by

$$I_{Di} = \beta_{pi} \left[ \left( V_{SGi} + V_{tpi} \right) V_{SDi} - \frac{1}{2} \left( 1 + \frac{\partial V_{tpi}}{\partial V_{BSi}} \right) V_{SDi}^2 \right]$$

(1)

where variables have their usual meanings, and *i*=1, 2, with  $\beta_{p_l} = \beta_{p_2} = \beta_p$ . If their source and drain voltages are equal, then the threshold voltages are also equal  $V_{tp_l} = V_{tp_2}$ , and the current difference is

$$I_{D1} - I_{D2} = \beta_p \left( V_{G2} - V_{G1} \right) V_{SD} \,. \tag{2}$$

Providing the equality of the source-to-drain voltages

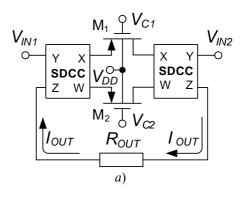

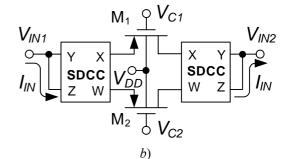

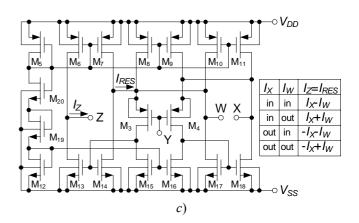

Fig. 1 Proposed voltage-controlled transconductor and floating resistor

a) Block diagram of the voltage-controlled transconductor,

b) Block diagram of the voltage-controlled resistor,

c) Summing-differencing current circuit.

$V_{SD1}=V_{SD2}=V_{SD}$  and the input voltage  $V_{IN}$  of the transconductor (resistor), (2) can be used to design a controllable transconductor (resistor). The block diagrams of the proposed VCT and floating VCR are shown in Figs. 1*a*) and 1*b*), respectively. Two SDCCs, two matched p-channel MOSFETs M<sub>1</sub> and M<sub>2</sub> with the common substrate, and two control voltages  $V_{CI}$  and  $V_{C2}$  are used in the proposed approach.

A new type of SDCC is shown in Fig. 1c). The output current flowing through the node Z is equal to the sum or to the difference of the currents flowing through the nodes X and W. The equality of the voltages at the nodes X and W is realized by the source followers M<sub>3</sub> and M<sub>4</sub> carrying the equal and constant currents  $I_{D3}=I_{D15}=I_{D16}=I_{D4}=const$ . Because no body effect occurs in M<sub>3</sub> and M<sub>4</sub>, their source-to-gate voltages are equal and constant  $V_{SG3}=V_{SG4}=const$ . The signs "+" and "-"in the table shown in Fig. 1c depend on the directions of the currents  $I_X$  and  $I_W$ . For example, the following equalities are valid for the first case ("in-in"):  $I_{D8}=I_{D9}, I_{D10}=I_{D11}, I_{D17}=I_{D18}, I_{D17}=I_W+I_{D10}+I_{D8}-I_{D3}+I_{RES}$  and  $I_{D18}=I_X+I_{D11}+I_{D9}-I_{D4}$ . Hence, the resulting current entering the node W is  $I_{RES}=I_X-I_W$ . The current follower M<sub>6</sub>-M<sub>7</sub>-M<sub>13</sub>-M<sub>14</sub> with  $I_{D6}=I_{D7}$  and  $I_{D13}=I_{D14}$  is involved to transfer the current  $I_{RES}$  toward the node Z. The currents  $I_{D6}=I_{D7}$ ,  $I_{D8}=I_{D9}$ ,  $I_{D10}=I_{D11}$ , and  $I_{D15}=I_{D16}$  are determined by the bias current formed by  $M_5$ ,  $M_{12}$ ,  $M_{19}$ , and  $M_{20}$ .

Taking into account (2) and Fig.1, the output current of the VCT (the input current of the floating VCR) is derived as

$$I_{Z} = I_{RES} = I_{X} - I_{W} = I_{D1} - I_{D2} = \beta_{p} \left( V_{C2} - V_{C1} \right) V_{IN}$$

(3)

where  $V_{IN}=V_{INI}-V_{IN2}=V_{SD1}=V_{SD2}=V_{SD}$ . The transconductance  $G_m$  and the resistance  $R_{EQ}$  of the proposed VCT and floating VCR, respectively, can be written as

$$G_m = \frac{1}{R_{EQ}} = \beta_p \left( V_{C2} - V_{C1} \right).$$

(4)

Linearity is not affected by the body effect in M<sub>1</sub> and M<sub>2</sub> because it occurs in an equal measure for both devices and cancels out. Assuming the simple quadratic model of the saturated M<sub>3</sub> and M<sub>4</sub>, the control voltage ranges can be found to be  $V_{Cl} < \min\{V_{INI}, V_{IN2}\} + (2I_{D4}/\beta_{P4})^{1/2} + V_{tp1} - V_{tp4}$  and  $V_{C2} < \min\{V_{INI}, V_{IN2}\} + (2I_{D3}/\beta_{P3})^{1/2} + V_{tp2} - V_{tp3}$ , with  $V_{tp1} = V_{tp2}$ ,  $V_{tp3} = V_{tp4}$ ,  $I_{D3} = I_{D4}$ , and  $\beta_{P3} = \beta_{P4}$ .

#### **3. SIMULATION RESULTS**

The operation of VCT and floating VCR shown in Fig. 1 has been simulated using SPICE with a level 3 MOS transistor model for AMIS ABN n-well CMOS process with 1.5 µm feature size ( $\lambda$ =0.8 µm) obtained by MOSIS. The *W/L* dimensions of the MOSFETs used are the following (in µm/µm): 6.4/1.6 (M<sub>1</sub>, M<sub>2</sub>), 8/1.6 (M<sub>12</sub>, M<sub>13</sub>, M<sub>14</sub>), 11.2/1.6 (M<sub>15</sub>, M<sub>16</sub>), 16/1.6 (M<sub>5</sub>, M<sub>8</sub>, M<sub>9</sub>), 24/1.6 (M<sub>17</sub>, M<sub>18</sub>), 184/1.6 (M<sub>10</sub>, M<sub>11</sub>). Resistor *R*<sub>OUT</sub>=12 kΩ, control voltage *V*<sub>C2</sub>=-1.5 V, and supply voltages of ± 1.5 V have been used.

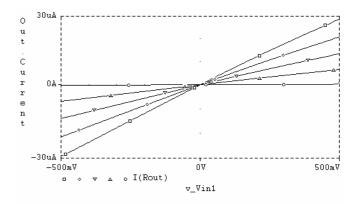

DC transfer characteristics of VCT for different values of the control voltage  $V_{Cl}$  are shown in Fig. 2. One of the inputs has been grounded,  $V_{IN2}=0$ . The input voltage  $V_{IN} = V_{INI}$  has been swept from -0.5 V to 0.5 V. The worst-case linearity error is lower than 1.4 %, except for  $V_{C1}=-1.5$  V, when it increases at the end of the input voltage range. DC transfer characteristics of VCR with the same values for  $V_{C1}$ ,  $V_{C2}$ , and  $V_{IN}$  are similar to those shown in Fig.2.

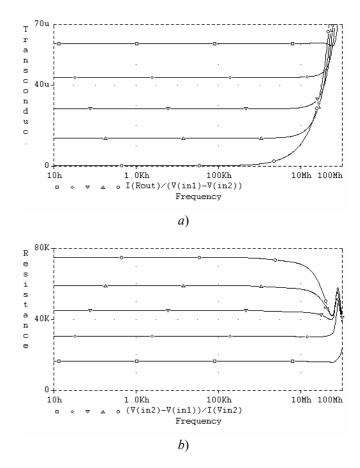

The frequency characteristics of VCT and VCR for

Fig.2: Output current versus input voltage of the transconductor ( $V_{C2}$ =-1.5 V)

$\Box V_{Cl} = -0.4 \text{ V},$   $\diamond V_{Cl} = -0.675,$   $\nabla V_{Cl} = -0.95 \text{ V},$  $\Delta V_{Cl} = -1.225 \text{ V},$

$\circ V_{Cl}$ =-1.5 V.

Fig. 3 Frequency characteristics of the transconductor a) and the resistor b)  $(V_{C2}=-1.5 \text{ V})$  $\Box$  a)  $V_{CI}=-0.4 \text{ V}$ , b)  $V_{CI}=-0.4 \text{ V}$  $\diamond$  a)  $V_{CI}=-0.675 \text{ V}$ , b)  $V_{CI}=-0.87 \text{ V}$

- $\bigtriangledown a) V_{Cl} = -0.95 \text{ V}, b) V_{Cl} = -1.06 \text{ V}$

- $\triangle a) V_{Cl}$ =-1.225 V, b)  $V_{Cl}$ =-1.16 V

- $\circ a) V_{Cl} = -1.5 \text{ V}, b) V_{Cl} = -1.23 \text{ V}$

different values of  $V_{CI}$  are shown in Figs. 3*a* and 3*b*, respectively. The  $\pm$  5 % frequency bandwidth of the transconductance is 70.5 MHz for  $V_{CI}$ =-0.4 V ( $G_m$ =60.4 µS).

The  $\pm$  5 % frequency bandwidths of the shown resistances are larger than 10 MHz, and is 74 MHz for  $V_{CI}$ =-0.4 V ( $R_{EQ}$ =16.6 kΩ). Finally, the total power consumption for both VCT and VCR is 1mW.

# 4. CONCLUSION

A voltage-controlled CMOS transconductor and floating resistor based on current difference of two nonsaturated MOSFETs with equal source-to-drain voltages have been discussed. The transconductance (resistance) can be both positive and negative, and independent of the devices' threshold voltages. They show good bandwidth and linearity, and a  $\pm 1.5$  V operation.

### REFERENCES

Y. Tsividis, Z. Czarnul, and S. C. Fang, "MOS transconductors and integrators with high linearity", *Electronics Letters*, vol. 22, pp. 245-246, 27<sup>th</sup> Feb. 1986.

- [2] K. Nagaraj, "New CMOS floating voltage-controlled resistor", *Electronics Letters*, vol. 22, pp. 667-668, 5<sup>th</sup> June 1986.

- [3] Y. Tsividis, *Operating and modeling of the MOS transistor*, 2<sup>nd</sup> edition, New York: McGraw-Hill, 1999.

**Sadržaj** – Predstavljeni naponom kontrolisan CMOS transkonduktor i otpornik baziraju se na razlici struja dva MOSFET-a u omskoj oblasti rada sa jednakim naponima sors-drejn. Upotrijebljen je novi tip kola za realizaciju operacija sabiranja i oduzimanja u strujnom domenu. Napon napajanja kolâ je  $\pm$  1.5 V. Simulacije ukazuju na nelinearnosti manje od 1.4 % za promjene ulaznog napona do  $\pm$  0.5 V, i frekventni opseg iznad 70 MHz, koji je definisan kao odstupanje od  $\pm$  5 % u odnosu na transkonduktanse i otpornosti pri jednosmjernim pobudama.

## NAPONOM KONTROLISAN CMOS TRANSKONDUKTOR I OTPORNIK NA BAZI RAZLIKE STRUJA

Nikša Tadić, Desa Gobović, Mirjana Banjević